- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT82V3202NLG (IDT, Integrated Device Technology Inc)IC PLL WAN EBU SGL 68-VFQFPN

IDT82V3202

EBU WAN PLL

Functional Description

18

September 11, 2009

3

FUNCTIONAL DESCRIPTION

3.1

RESET

The reset operation resets all registers and state machines to their

default value or status.

After power on, the device must be reset for normal operation.

For a complete reset, the RST pin must be asserted low for at least

50 s. After the RST pin is pulled high, the device will still be in reset

state for 500 ms (typical). If the RST pin is held low continuously, the

device remains in reset state.

3.2

MASTER CLOCK

A nominal 12.8000 MHz clock, provided by a crystal oscillator, is

input on the OSCI pin. This clock is provided for the device as a master

clock. The master clock is used as a reference clock for all the internal

circuits. A better active edge of the master clock is selected by the

OSC_EDGE bit to improve jitter and wander performance.

In fact, an offset from the nominal frequency may input on the OSCI

pin.

This

offset

can

be

compensated

by

setting

the

NOMINAL_FREQ_VALUE[23:0] bits. The calibration range is within

±741 ppm.

The performance of the master clock should meet GR-1244-CORE,

GR-253-CORE, ITU-T G.812 and G.813 criteria.

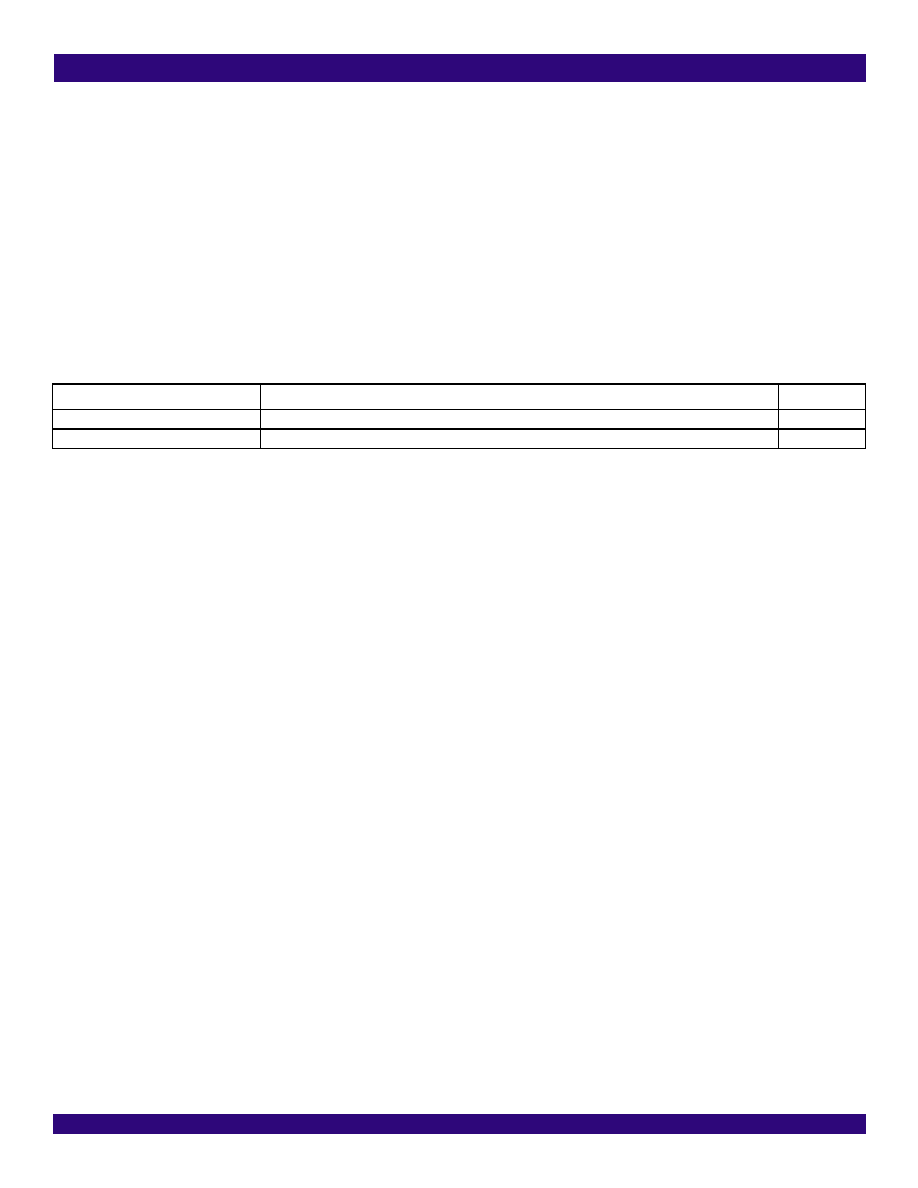

Table 2: Related Bit / Register in Chapter 3.2

Bit

Register

Address (Hex)

NOMINAL_FREQ_VALUE[23:0]

NOMINAL_FREQ[23:16]_CNFG, NOMINAL_FREQ[15:8]_CNFG, NOMINAL_FREQ[7:0]_CNFG

06, 05, 04

OSC_EDGE

DIFFERENTIAL_IN_OUT_OSCI_CNFG

0A

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT82V3255TFG

IC PLL WAN SMC STRATUM 3 64-TQFP

IDT82V3280APFG

IC PLL WAN SE STRATUM 2 100TQFP

IDT82V3285AEQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3285EQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3288BCG

IC PLL WAN 3E STRATUM 2 208CABGA

IDT82V3355EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDT82V3358EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDTCSPT857DNLG8

IC PLL CLK DVR SDRAM 40-VFQFPN

相关代理商/技术参数

IDT82V3202NLG8

功能描述:IC PLL WAN EBU SGL 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3202NLGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:EBU WAN PLL

IDT82V3255

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255_08

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255DK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255DKG

功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3255DKG8

功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3255EDGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL